|

OTG (JTAG)

| |

| Galla | Дата: Среда, 02.02.2022, 11:53 | Сообщение # 1 |

Группа: Администраторы

Сообщений: 304

Статус: Offline

| Шапка в процессе редактирования

|

| |

| |

| Galla | Дата: Понедельник, 11.04.2022, 18:11 | Сообщение # 2 |

Группа: Администраторы

Сообщений: 304

Статус: Offline

| Интерфейс JTAG? — Это очень просто

Многие знакомы со словом «JTAG», но знакомство это скорее всего поверхностное. В этой статье я хочу перевести Вас на новый уровень, так сказать «во френдзону». Возможно, для многих я не открою ничего нового, но надеюсь тем, кто давно хотел ознакомиться, будет интересно почитать. Итак, от винта.

Введение

В 1985 сформировалась группа производителей электроники — JTAG (Joint Test Action Group). Для решения проблем тестирования в 1990 был выдвинут промышленный стандарт — спецификация IEEE Std 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture). В этом же году Intel вывел в свет первый процессор с JTAG — 80486. С тех пор стандарт постоянно модифицируется и, в данный момент, последняя версия датируется 2013 годом.

«А какие же это проблемы с тестированием?»,- спросите Вы. Ну как же! Мало удовольствия прыгать с осциллографом по выводам микросхемы, особенно если их много больше двух! Стандарт позволяет значительно упростить жизнь за счет встраивания специальной архитектуры в современные чипы, обеспечивающей доступ к выводам (точнее, к специальным блокам ввода-вывода) с помощью 4-х проводного последовательного интерфейса. Эта архитектура позволяет не только контролировать их состояние, но и управлять ими. Таким образом можно обойтись без громоздких пробников с физическим контактом и насладиться всей прелестью этапа отладки цифровых микросхем или устройств уровня печатной платы.

Стандарт используют как для целей внутрисхемного программирования и отладки программ, так и при работе с корпусированными микросхемами. Он же используется для проверки на качество припайки микросхем к плате, межплатного и внутристоечного монтажа плат и блоков. Также надо сказать ему спасибо за восстановление закирпиченных по неосторожности мобильных устройств.

И как же работает?

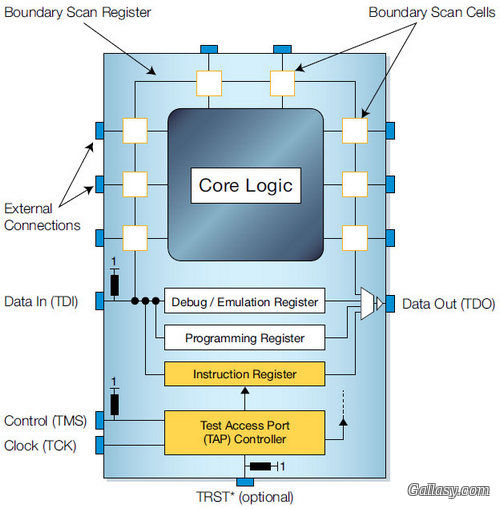

Механизм граничного сканирования заключен, всего лишь, в сдвиговом регистре (Boundary Scan), подключенном между выводами микросхемы и ядром, и мультиплексоре который подключает в нужный момент этот регистр. Каждому конкретному выводу соответствуют так называемые «ячейки».

В состав ячейки входит один триггер регистра граничного сканирования и мультиплексора выбора данных. Ячейки могут быть разных типов в зависимости от вывода микросхемы и команд интерфейса, т.е. зависит от производителя той или иной микросхемы. Производители не придерживаются строго стандарта и, поэтому, развелось множество модификаций.

На рисунке представлена одна из разновидностей ячейки. PI, PO — параллельные вход и выход, SI,SO — последовательные.

Сигналы на регистр микросхемы попадают через мультиплексор, который позволяет считывать как состояния выводов ядра микросхемы (инструкция INTEST), так и данные, поступающие извне на сдвиговый регистр (инструкция EXTEST). Разновидности инструкций и их функциональность опять же меняются от желаний производителя, но существуют так называемые обязательные:

EXTEST — инструкция, позволяющая за счет установки логических значений на рабочих контактах электронных компонентов проверить внешние цепи, имеющие непосредственное отношение к тестируемому компоненту.

INTEST — инструкция обеспечивает возможность установки логических значений внутри микросхемы, то есть на входах ядра, тем самым проверяя его.

SAMPLE_PRELOAD — позволяет тестировать ядро электронного элемента в статическом режиме, устанавливая значения логических уровней на границе его выходных буферов.

BYPASS — инструкция, при которой наш регистр граничного сканирования «схлопывается» в один триггер. При этом данные со входа (TDI) на выход (TDO) передаются с задержкой в один такт частоты синхронизации интерфейса (TCK). Этот режим позволяет эффективно использовать возможности последовательного интерфейса при организации длинных последовательно объединенных цепочек.

IDCODE — инструкция выдвигает на выход значение встроенного 32-битного регистра с идентификаторами производителя, модели и версии устройства.

Сигнальные линии интерфейса

Как уже говорилось выше, интерфейс JTAG имеет следующие сигнальные линии:

TDI — Test Data Input — сигнал данных на вход, данные задвигаются по переднему фронту TCK.

TDO — Test Data Output — выход последовательных данных JTAG, выдвигаются по заднему фронту TCK, должен находиться в третьем состоянии — Z — когда данные не передаются.

TMS — Test Mode Select — сигнал управления TAP — контроллером.

TRST — Test Reset — не всегда есть, так как ресета можно добиться удерживая некоторое время TMS = 1, активный уровень сигнала — 0.

TCK — Test Clock — тактовая частота.

JTAG — синхронный интерфейс, сигналы принимаются по переднему фронту синхроимпульсов младшими битами вперед и только в течении состояний TAP — контроллера Shift-DR \ Shift-IR. Выходные данные выдвигаются по заднему фронту.

TAP — контроллер

Мы добрались до самой сути JTAG, а именно — управляющий работой автомат. С его помощью собственно и живет всё вокруг. Автомат имеет 16 состояний. Управление интерфейсом осуществляется путем воздействия на автомат посредством сигнала TMS. Переходы происходят по переднему фронту сигнала TCK. Чтение и запись данных происходят одновременно. Ниже привожу иллюстрацию работы, взятую из документации микросхем фирмы Altera.

Диаграмма переходов автомата, управляющего режимами TAP

Состояния диаграммы переходов:

Test-Logic-Reset – исходное состояние;

Run-Test/Idle – переходное состояние контроллера при выполнении тестов или ожидании следующей

команды;

Select-IR, Select-DR – состояние, после которого будет производиться тестирование команд, данных;

Capture-IR, Capture-DR – состояние приёма команд, данных;

Shift-IR, Shift-DR – состояние сдвига команд, данных;

Exit1-IR, Exit2-IR – выход из режима работы с командами;

Exit1-DR, Exit2-DR – выход из режима работы с данными;

Pause-IR, Pause-DR – состояние паузы;

Update-IR, Update-DR – состояние перезаписи данных в выходные регистры.

DR — действия происходят над данными, IR — соответственно над инструкциями.

Исходное состояние, в котором находится автомат после включения, это Test-Logic Reset. Пока сигнал TMS имеет значение «лог.1», состояние автомата остается неизменным. В этом состоянии, по умолчанию, выбрана инструкция IDCODE или BYPASS.

Сигнал сброса TRST не является обязательным, поэтому для сброса автомата в исходное состояние применяют следующую процедуру. Необходимо подать на вход TMS сигнал высокого уровня и удерживать его не менее 5 тактов частоты TCK. Если сигнал TMS будет установлен хостом в низкий уровень, то автомат перейдёт к состоянию Run-Test/Idle (активное состояни, в котором ничего не происходит). Обычно из этого состояния можно перейти в состояние Select-IR, для того чтобы загрузить в контроллер новую инструкцию. Но если на вход сигнала TMS подействует не сигнал, подаваемый от хоста, а помеха низкого уровня, то, как и в предыдущем случае, автомат перейдёт в состояние Run-Test/Idle. Если же кратковременная помеха (длительностью не более одного периода синхрочастоты) прекратится, то автомат через три такта снова вернётся в исходное состояние – Test-Logic Reset.

Чтобы загрузить в контроллер новую команду, надо из состояния Run-Test/Idle перевести автомат в состояние Select-IR, Capture-IR, Shift-IR. Затем необходимо «продвинуть» в цепочку данных новую команду, а потом перевести автомат через состояния Exit1-IR, Update-IR и снова в Run-Test/Idle. Логика работы с данными такая же. Нужно учитывать, что сигнал высокого уровня при переходе из состояний Shift-IR\DR подается вместе с последним битом информации.

|

| |

| |

| Galla | Дата: Понедельник, 11.04.2022, 18:18 | Сообщение # 3 |

Группа: Администраторы

Сообщений: 304

Статус: Offline

| Что такое JTAG и как это применить для тестирования печатных плат?

JTAG – это нечто большее, чем просто отладка и перепрограммирование микросхем

JTAG is NOT JUST a technology for debugging and programming

Если Вы применяли какие-либо инструменты, использующие JTAG, то Вы уже знакомы с этим интерфейсом. Например, процессоры часто используют JTAG для доступа к своим отладочным функциям, также все ПЛИС используют JTAG для перепрограммирования.

JTAG – это НЕ ТОЛЬКО отладка процессоров.

JTAG – это НЕ ТОЛЬКО программирование ПЛИС/CPLD.

Название JTAG чаще всего ассоциируется с инструментами отладки и перепрограммирования микросхем. Однако, в этих инструментах реализована только часть возможностей JTAG.

Boundary Scan Register (BSR) for JTAG testing

Эта часть возможностей, известная под названием Test Access Port или, сокращённо, TAP, является частью стандарта IEEE Std. 1149.1. Этот стандарт был разработан для тестирования сборок печатных плат (Printed Circuit Board Assemblies – PCBA) без необходимости доступа на так называемом «низком» (физическом) уровне, который требуется для анализа «сложных» случаев. Стандарт также не предусматривает разработку и использование специфических функциональных тестов. Изначально TAP был разработан только для взаимодействия с дополнительными регистрами, специально вставляемыми в микросхему с целью реализации данного метода тестирования.

Однако достаточно быстро производители микросхем заметили потенциал использования TAP и для других целей, например, для доступа к регистрам, предназначенным для отладки и перепрограммирования микросхем.

Теперь в микросхемы добавляется специальный регистр для тестирования через JTAG под названием Boundary Scan Register (BSR). Как и подразумевает название этого регистра, отдельные его части (или, по-другому, ячейки (Cells)) являются «пограничными» для микросхемы, так как располагаются между функциональным ядром и контактами корпуса микросхемы. По этой причине тестирование через JTAG часто называют пограничным сканированием (boundary scan).

Как технология пограничного сканирования, реализуемая стандартом JTAG, используется для тестирования печатных плат?

Ячейки регистра пограничного сканирования (Boundary Scan Register) могут работать в одном из двух режимов: 1) функциональный режим – ячейки не влияют на работу прибора, прибор работает в своём обычном виде; 2) тестирующий режим – ячейки отсоединяют функциональное ядро микросхемы от контактов корпуса. Тестирующий режим используется для управления значениями на контактах корпуса микросхемы (и в соответствующих цепях печатной платы), а также для считывания значений с подключённых цепей печатной платы.

Отключение функционального ядра микросхемы существенно упрощает разработку тестов, так как использование пограничного сканирования (boundary scan) позволяет не разрабатывать программу для микропроцессора или прошивку для ПЛИС и не включать прибор в «рабочем» режиме. Механизм управления и наблюдения за контактами корпуса микросхемы через четырёх-контактный TAP, JTAG интерфейс позволяет получить низкоуровневый доступ к контактам микросхемы для физического тестирования печатной платы.

Существует два способа тестирования печатной платы при помощи пограничного сканирования (boundary scan). Первый способ – тест соединений (connection test). Он даёт хорошее покрытие, особенно для поиска таких неисправностей, как замыкания. Этот способ использует только возможности микросхемы с поддержкой JTAG, при этом тестируются соединения (например, пропайки) и цепи, а в случае применения системы XJTAG, тестируются ещё и логические функции платы. Второй способ – использование микросхемы с поддержкой JTAG для взаимодействия с микросхемами без поддержки JTAG, такими как DDR RAM или Flash память.

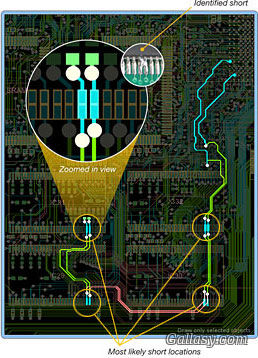

Что такое тест соединений (connection test) через JTAG?Example of faults tested for by the XJTAG connection test

Тест соединений (connection test) проверяет, соответствует ли изготовленная печатная плата исходному проекту, а также наличие на ней не предусмотренных проектом разрывов цепей или лишних замыканий.

Если согласно проекту какие-то контакты микросхемы должны быть соединены где-то на плате, то можно проверить факт наличия соединения, подавая значения на один из контактов и считывая с других. Если согласно проекту контакты микросхемы НЕ соединены, то можно проверить, нет ли между ними лишнего замыкания, подавая на один из них значения и проверяя, что на остальные это не влияет.

Кроме того, тест соединений (connection test) позволяет обнаружить отсутствие нужных подтягивающих резисторов, и «залипания» сигналов. Это также делается путём выставления на контактах определённых значений и сравнения считанных значений с заданной таблицей истинности.

Система XJTAG на основе нетлиста печатной платы и информации, считанной с поддерживающих JTAG микросхем, полностью автоматически генерирует тестовые вектора для проведения теста соединений (connection test) всей платы.

Что же делать с остальными микросхемами на плате, которые не поддерживают JTAG?

Как правило, основные микросхемы на плате, такие как процессоры и ПЛИС, поддерживают JTAG, но существует множество вспомогательных микросхем, которые JTAG не поддерживают. Как пример можно привести такие микросхемы, как ЦАП, АЦП, DDR, SDRAM, SRAM, Flash, Ethernet контроллеры, температурные сенсоры, генераторы частот и многое другое.

Тест соединений (connection test) позволяет проводить тестирование на замыкания цепей между микросхемами с поддержкой JTAG и микросхемами без поддержки, при этом достигается хорошее покрытие. Однако протестировать обрывы в таких цепях уже не получится.

С целью тестирования на наличие обрывов цепей между микросхемами с поддержкой JTAG и микросхемами без таковой, требуется использовать так называемые функциональные тесты. Если функциональные тесты пройдены, то это означает, что обрывов быть не может. Функциональные тесты могут быть как очень простыми, например, включение светодиода и ожидание подтверждения от оператора, что светодиод действительно загорелся, так и посложнее, например, запись данных в память, считывание их же и сравнение считанных данных с ожидаемыми.

Насколько сложно подготовить JTAG тесты?

При помощи библиотеки тестов для стандартных микросхем без поддержки JTAG, поставляемой с системой XJTAG, возможна подготовка и запуск набора функциональных тестов без необходимости программирования. Библиотека тестов содержит тесты как для простых элементов, таких как резисторы и буферные элементы, так и для сложных микросхем, таких как память DDR3 и так далее.

Т.к. пограничное сканирование (boundary scan) отключает контакты корпуса микросхемы от функционального кремниевого ядра, единая тестовая модель может быть использована для управления периферийными микросхемами вне зависимости от того, какая микросхема с поддержкой JTAG использована.

Как правило, в печатную плату не требуется вносить никаких изменений, так как большинство плат уже содержат JTAG контакты для отладки процессоров или программирования ПЛИС.

Что ещё нужно для использования микросхем с поддержкой JTAG?

Для тестирования печатной платы при помощи пограничного сканирования (boundary scan) требуется для каждой микросхемы с поддержкой JTAG скачать с сайта производителя микросхемы так называемый BSDL-файл – Boundary Scan Description Language. Это текстовый файл, описывающий назначения ножек корпуса микросхемы.

Используется ли JTAG тестирование в основном на производстве?

Не совсем. Одним из важнейших преимуществ тестирования через пограничное сканирование (boundary scan) является тот факт, что из дополнительного оборудования требуется только JTAG контроллер. Другие технологии тестирования, такие как летающие щупы (flying probe), рентгеновское сканирование, многозондовое тестирование (bed-of-nails) и так далее требуют наличия дорогостоящего оборудования, которое не всегда доступно.

Использование пограничного сканирования (boundary scan) при первом тестировании позволяет проводить тестирование более уверенно, так как не требует включения платы в основной режим работы и даже может быть выполнено ещё до окончания разработки «прошивки». Эти же тесты, разработанные при проектировании, могут быть использованы и на производстве.

Почему следует использовать пограничное сканирование через JTAG для тестирования печатных плат?

BGA

С увеличением доли микросхем, реализованных в корпусе BGA (Ball Grid Array), применение традиционных систем тестирования печатных плат, таких как многозондовое тестирование (bed-of-nails) или летающие щупы (flying probe) становится всё более ограниченным, так как «внутренние» контакты физически недоступны.

Пограничное сканирование (boundary scan) на основе JTAG при помощи простого «четырёхконтактного» интерфейса позволяет произвольно управлять контактами корпуса микросхемы с поддержкой JTAG, в том числе считывать значения, не имея к контактам физического доступа.

Стенд

В процессе проектирования и отладки временны́е и денежные затраты на разработку/приобретение испытательных/отладочных стендов могут быть очень существенными, а в некоторых случаях и превышать затраты на само проектирование. Во многих случаях использование пограничного сканирования (boundary scan) позволяет вообще отказаться от применения испытательного стенда, а в остальных случаях подойдет и значительно более простой и дешёвый стенд.

Малые партии

В случае, когда у компании имеется много проектов плат, выпускаемых малыми партиями, задача удешевления тестового оборудования особенно актуальна. Единственно приемлемым вариантом в данном случае является покупка системы «летающие щупы» (flying probe), но если цена при этом делится на все проекты, то временны́е затраты на подготовку теста для каждого проекта остаются неприемлемыми. Использование пограничного сканирования (boundary scan) позволяет ускорить подготовку теста для каждого проекта, при том, что покупка дорогостоящего тестового оборудования теперь не требуется.

Стоимость разработки теста

Так как разные микросхемы (процессоры и ПЛИС) взаимодействуют с периферией разными способами, разработка традиционного функционального теста отдельно для каждой платы является очень затратной. Пограничное сканирование (boundary scan) существенно сокращает стоимость разработки тестов благодаря упрощённому способу управления контактами корпуса микросхемы для взаимодействия с остальными компонентами на плате. А унифицированный интерфейс JTAG позволяет формировать отдельные тесты как библиотечные элементы и использовать их в разных проектах вне зависимости от применяемых микросхем с поддержкой JTAG.

И для тестирования и для программирования

JTAG часто применяется для программирования микросхем (ПЛИС) на плате в процессе производства. А если к программированию дополнительно добавить тестирование платы через так называемое пограничное сканирование (boundary scan), то получится существенно сэкономить время и упростить производство.

Использование на производстве тех же тестов, которые применялись при проектировании

Обычно для тестирования изделий на производстве применяется большое дорогостоящее оборудование. Всё, что требуется для применения пограничного сканирования (boundary scan) через JTAG – это контроллер XJLink, размерами сопоставимый с компьютерной мышью.

Удобная диагностика неисправностейShort-circuit diagnosed with XJRunner

Пограничное сканирование (boundary scan) через JTAG, в отличие от специально разработанных функциональных тестов, позволяет получать информацию о точном месте возникновения неисправности, что очень помогает при восстановлении платы. А применение системы XJTAG ещё и позволяет визуализировать место неисправности на плате и указать точное место в принципиальной схеме.

Восстановление нерабочих плат, где функциональные тесты бессильны

Пограничное сканирование (boundary scan) через JTAG можно использовать на плате, где не работает ничего, кроме самого JTAG интерфейса. Если плата не включается, то провести традиционные функциональные тесты не получится. Простейшая неисправность в таких элементах на плате, как память или генератор синхросигнала не позволят применить функциональный тест, но легко обнаруживается при помощи JTAG.

|

| |

| |

|